• A Computer is a Complex System

Low-Level components require detailed, properly timed operating instructions. Without built-in complexity management:

- Programmer productivity would be very low.

Need to shield programmers from the complexity of the hardware.

- End User knowledge would have to be very high.

Need to present users with a simpler interface or simpler virtual machine.

- A Computer System is a synergistic combination of Hardware + Software.

Without software, a computer is useless, uncoordinated pieces of electronic parts.

- There are two major types of computer software:

- 1) Application Programs which solve problems for users in various domains.

- 2) System Programs which manage the operation of the computer itself.

- A Computer System has 4 major components:

- 1) Users

- 2) Application Programs

- 3) Systems Programs

- 4) Hardware

- Most digital computers operate under the stored program concept.

Program is stored in the same memory that contains the data.

Generally attributed to von Neumann.

An OS is Software but has a tighter integration with the hardware.

Software can be run in two modes:

User Mode: Hardware does not prevent user from making modifications.

- e.g.) User can write his own compiler, or use another commercial compiler.

- Kernel Mode or Supervisor Mode: S/W protected from user tampering by H/W.

- e.g.) User cannot modify or write his own disk interrupt handler.

Therefore,

Command Interpreters, Compilers, and Editors are *not* considered part of the OS. These are typically supplied by computer manufacturer, but run in user mode.

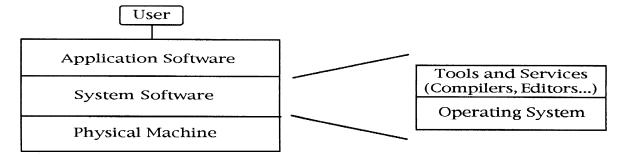

Structure of a Computer System and The Components of System Software

- An Operating System serves two roles:

- 1) As a Resource Manager (Bottom-Up View).

Goal is to Make the computer system efficient.

This is especially important for large shared multi-user systems.

Provide orderly/controlled allocation of CPU, memory, and I/O to competing jobs.

e.g.) Manage 3 jobs attempting to write to the same printer at the same time.

Controls all of the computer's resources.

OS allocates resources to specific programs and users fairly and efficiently.

Gets hardware subsystems and application software to cooperate harmoniously.

OS Serves as the interface between application software and hardware.

Provides the base upon which application programs can be written.

Alternative view and name:

"OS" = "Control Program" which controls user programs, I/O Devices, etc.

e.g.) CP/M: Control Program for Microcomputers

2) As a Virtual Machine (Top-Down View).

Goal is to Make the computer system convenient to use.

Especially important for small personal computers.

Hide the low-level machine complexity from the programmer and user.

Provide programmer with simple, high-level abstractions to deal with.

Hides the truth about the hardware from the programmer.

e.g.) Disk becomes a collection of named files; not records/blocks/sectors.

Provides a more convenient set of instructions to program in and to work with.

e.g.) "READ FILE" vs. "Move Disk Head to Track 129 of Drive 2, Wait 6ms"

Provide the user with a virtual machine that is easier to program than raw H/W.

OS acts as an interface between a user and the computer hardware.

OS provides reasonably high-level services with unreasonably low-level H/W.

• Technology has changed operating systems design.

**Before**: Expensive, large, time-shared mainframes.

Resource Optimization and Accounting were important.

Now: Cheap, small, single-user personal computers and workstations.

User-friendliness is most important. Hardly any accounting.

Note: Convenience and Efficiency are often contradictory goals.

• The most Important System Program is the Operating System.

Question: "What is an Operating System?"

Answer (1970's): "All Programs Written and Supplied by IBM"

Answer (1990's): "All Programs Written and Supplied by Microsoft"

Operating Systems have continually evolved.

Question: "What is a popular, state-of-the-art Operating System?"

Answer (1970's): "IBM/OS360 JCL, DEC/VAX-VMS, DOS" [Text Based]

Answer (1980's): "Macintosh, Windows 3.1" [GUI Based]

Answer (1990's): "Mac/System 7" [Networking, File Sharing]

Answer (8/24/95): "Windows 95" [Plug & Play, Internet WWW]

Answer (1996 ?) "Mac/System 8" [PowerPC Optimization]

• An Operating System has four major components:

Viewed as concentric circles with hardware at the core, working away from center. This is also the order in which we will study material for our class.

1) Memory Management.

Memory is most expensive hardware in computer.

Need Fast Speed and Large Size and Low Cost.

The OS must utilize and manage the memory system effectively.

2) Processor Management.

Mainframe may cost \$500 per hour.

The OS must have efficient Scheduling Algorithms for the CPU.

3) Resource and Process Management.

Processes need to share resources, communicate, coordinate, and synchronize

4) File System and Input / Output Management.

The OS should organize information and protect it.

The OS must schedule and coordinate Device Drivers for I/O.

Note: In a strictly hierarchical sense, a given level can only call an inner level.

But, This is not the case with the OS concentric circle view.

Circle view helps identify which part of OS is closest to the low-level hardware.

This is more of a layering approach to organization.

We look at one layer at a time.

- Why Study Operating Systems ?

- To create high-performance computer systems at a cost-effective price,

Knowledge of the H/W + S/W design alternatives and tradeoffs is important.

- Every computer specialist should know something about operating systems.

Can help a software engineer write more efficient programs.

Can help hardware engineer design better machines.

• Because operating systems work at the hardware / software boundary,

Some details of the hardware need to be discussed to understand OS algorithms.

## Outline of Major topics:

- Memory Management

Hierarchy

Locality of Reference

Virtual Memory

Paging, Segmentation

Replacement Algorithms

- Processor Management

Scheduling

Properties of Distribution

Multi-Level Scheduling

- Resource Management

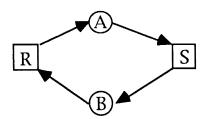

Deadlock

**Mutual Exclusion**

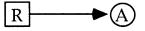

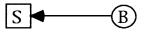

**Resource Graphs**

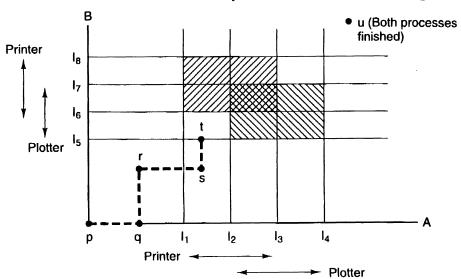

Resource Trajectories

Avoidance vs. Prevention

Avoidance/Prevention Schemes

Hierarchy, Ordering of resources

**Bankers Algorithm**

- Process Management

**Concurrent Processes**

**Communication Primitives**

Semaphores

Critical Regions

Test and Set

Producer/Consumer

Reader/Writer

- File Management

Non-Hierarchical vs. Hierarchical

**Protection**

Authentication, Control Policies Capabilities vs. Access Lists

- Virtual Machines

**Emulation**

- Performance

Reliability / Fault-Tolerance

- A computer system should satisfy several general design objectives:

- 1) Provide an "easy to use" (user-friendly) appearance in S/W and H/W operation.

- 2) Provide low-cost computing by sharing resources and information.

- 3) Provide an efficient environment for program development, debugging, execution.

- These functions must be provided by the system as integral characteristics.

- The system software that provides these functions is called the Operating System.

- Therefore, the basic functions performed by the OS must include:

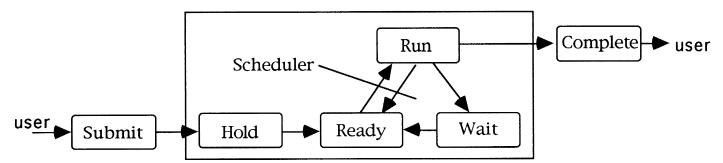

Job Scheduling

Error, I/O, and Interrupt handling

Resource control

**Protection**

Good user interface

Accounting of computing resources

In general, an OS today assists in the construction and execution of user programs.

Virtually all phases of program development and execution are supported by OS.

Example: PL/1 execution environment

A PL/1 compiler needs OS to read source input, and print its output listing. Object code produced by PL/1 compiler needs run-time environment.

- e.g.) ALLOCATE and FREE need the OS's Memory management.

- e.g.) ON CONDITIONS need the OS's interrupt handlers.

- How the need for these functions arose can be seen in the history of computers.

- The History and Evolution of Operating Systems

Focus on evolution of: 1) Efficiency of Resource Allocation, and 2) Ease of Use.

- Before 1950's: The Age of Hands-on operation.

Job-by-job processing.

No operating system.

Operation of loading and running a user program performed entirely by human.

Each programmer operated the computer personally (loaded cards, pushed buttons).

Typical tedious sequence of tasks:

Place the source program cards in the card reader.

Initiate a program to read in the cards.

Initiate a compiler to compile the source program.

Place the data cards, if any, in the card reader.

Initiate execution of the compiled program.

Remove results from the line printer.

Single User had one-at-a-time exclusive access to the entire machine's resources.

Problem: Very uneconomical since expensive hardware was being underused.

• 1950's: The Age of Job Sequencing Monitors (Early Batch Processing). Computers getting faster and more expensive.

Too costly to wait for a slow human to manually load his jobs in and push buttons.

- First improvement:

Let machine itself read-in, compile, load, and execute a program automatically. Requires that part of the machine be dedicated for this control (embryonic OS).

- This allowed a series of jobs prepared in advance to be executed sequentially.

Allowed automatic transition from one job to the next without long loading times.

- Monitor had to provide inherent protection functions against errors such as: Limitation on processor times.

Run time limits to prevent an infinite loop from blocking whole system. Supervision of input-output.

Page limits to stop I/O loops.

Protection of memory area reserved for the monitor.

Avoids accidental/deliberate modification of kernel by a user program.

- Problem: Processor was wholly occupied during execution of input-output.

- 1960's: The Age of Batch Processing Systems (Off-Lining).

- Use two systems:

- 1) Main computer for program execution.

Executes jobs read off a magnetic tape; writes results back to magnetic tape.

- 2) I/O computer(s) for preparing input onto or printing results off of magnetic tape.

Took information from card reader and wrote it to magnetic tape.

This I/O computer could be operated in parallel with the main computer.

- Allows Main computer to process at full speed without having to wait for slow I/O. Requires an extension to the embryonic OS of 1950's.

Need routines for the coding and packing of data on magnetic tape.

- Off-Lining only reduced I/O dependency, but did not eliminate it.

Main computer was no longer constrained by the speed of the card reader.

But still constrained by speed of a tape reader (which is faster than card reader).

- Example: IBM Fortran Monitor System (FMS).

- 1970's: The Age of Spooling, Multiprogramming, and Time-Sharing.

Primarily Large (IBM) Mainframe technology.

Computer technology "takes off" and many improvements in H/W and S/W occur.

- One of the first improvements to early batch systems was spooling.

Spool: Simultaneous Peripheral Operation On Line.

Disk Drive Technology enables mass storage at fast access speeds.

Spooling allows CPU to read in future job(s) while processing current one.

Thus, computer can rapidly switch to a new job when current job completes.

Execution order of spooled batches can even be different from the order read in.

Multiprogramming gives each user the illusion of having whole system to himself.

Idea of concurrency (either real or imagined) enables interactive time-sharing.

Significantly increased operating system complexity.

In order for all jobs to be ready to run, they must all be kept in memory. Rapid context switch mechanisms needed.

Also, need to provide for memory sharing and mutual protection of programs.

- Timesharing allows interactive, on-line communication between user and computer.

Main advantage: Enabled programmer to interactively debug program.

Much more productive than static snapshot dumps from a batch system.

- Also, to eliminate I/O dependency (not just reduce it), overlap I/O with processing. Channels and interrupts were therefore developed (e.g. printer controllers)

- Main Characteristics of machines in the 1970's:

Specialized processors were used for information transfer.

Enabled system to perform I/O concurrently with CPU processing.

Memory could be shared between several jobs.

Enabled many jobs to be 'active' so CPU can choose from among several jobs. Users were given an interactive mode of operation.

Each user had the "whole machine to himself" at a fraction of the cost.

- These characteristics required the operating system to be able to:

Buffer input/output from slower (factor of 10,000) devices as compared to the CPU.

OS had to store large amounts of temporary input and output.

Allow one job to use CPU while another performs I/O.

OS should keep the expensive CPU busy at all times to maximize throughput. Reorder jobs to minimize overall system response times.

OS should not let one large job stop many small jobs from ever executing. Keep accurate accounting of resources used by each process.

Total time in system is not equal to total CPU time and memory expended.

- Example: IBM OS/360.

Two to Three orders of magnitude larger than FMS.

Millions of lines of assembly language written by thousands of programmers.

Continuous stream of new releases were required to patch thousands of bugs.

Described as "a herd of prehistoric beasts stuck in a tar pit".

• 1980's: The Age of Workstations, Personal Computers.

Microprocessors are introduced giving increased performance at lower costs.

Prices for machines fall to within reach of the average household.

- Emphasis shifts towards "personal", user-friendly computing.

Graphical User Interfaces for the masses replace cryptic command-line prompts.

Advances in both H/W and S/W technology were needed to "bring machines home".

Microprocessor Hardware brought down the cost making it affordable.

Operating System Software brought down the complexity for the 'average user'. Desirable qualities in a personal computer include:

- Simplicity in use.

- Ease of extension by adding new utility programs (Setup program).

- Ease of extension by adding, adapting to new peripherals (e.g. Plug and Play).

- Efficiency (since performance of hardware is low, need to use it efficiently).

- Reliability.

- 1990's: The Age of Networks (especially Internet), Distributed systems, Laptops, PDAs

Portable devices require the need to "keep in touch" from anywhere in world.

Emphasis is on communications protocols (modems), file sharing/synchronization.

OS starts to handle some aspects of Networking (e.g., AppleTalk, Internet Access).

OS even responsible for handwriting recognition in PDAs.

- In summary, operating systems continue to grow in responsibility.

As computer power grew, resources required more sophisticated management.

Keeping track of resource usage and status became increasingly complex.

Therefore, the OS became, and will continue to become, more and more complex.

- We shall emphasize the study of algorithms for:

- Managing main and auxiliary memory devices.

- e.g.) Memory Manager.

- Managing, coordinating, and scheduling CPU and I/O processes.

- e.g.) Process Scheduler.

- Managing information flow among various devices/processes in a computer system.

e.g.) Resource Manager, Interprocess Communication.

- We will study these algorithms from the perspective of both:

- Small systems (PC, workstations).

- Large systems (mainframes, distributed computer networks).

- Some algorithms meet acceptable standards, some are awkward, some are elegant.

Performance issues are also discussed, including:

Response Times (in multi-access systems).

Turn-around time for jobs (in batch systems).

Central Processor Unit Utilization time.

Resource Utilization.

=> A good OS increases efficiency and consequently decreases cost of using computers.

### Memory

Digital computer is based on the stored program concept.

Depends on memory to store both data and instructions needed for its operation. Even the Operating System resides in Memory.

- => Memory is a critical resource in the computer and it needs to be managed.

- Current technology trend and applications demand even faster and larger memories.

Parameters that affect the memory design of a system includes:

- Speed of the processor.

- Speed of the I/O devices.

- Expected application type and program size. (e.g., multimedia)

- Expected degree of concurrency in a multiprogramming environment.

- Expected number of instructions needed to process a transaction.

(e.g., RISC architectures need more instructions per transaction.)

- Size required for underlying systems software (e.g., Resident OS code).

- The problem:

There is a disparity between CPU logic speed and memory speed.

Logic advances proceeded at a faster rate than advances in memory.

The CPU can usually process instructions and data faster than they can be fetched from compatibly priced conventional main memory units.

- => Main Memory is the bottleneck in terms of system speed and cost.

Speed of computer is limited by time needed to store and retrieve information.

Cost of a system is determined by the data storage capacity of its memory.

- The importance of good memory design cannot be overstated.

It can determine the useful lifetime of a machine.

Bell and Strecker [1976]:

"There is only one mistake that can be made in computer design that is difficult to recover from -- not having enough address bits for memory addressing and memory management".

Address size is hard to change since it determines width of all H/W data items.

- e.g.) Registers, program counters, effective address arith., bus width.

- => If there are no plans made to expand the address size from the start,

Then the end of the computer family will occur when the address size changes.

- Considerable effort is often devoted to the development and improvement of memory.

The Memory Manager of the Operating System plays a critical role.

Goal: Make up in S/W what cannot be attained in memory H/W technology.

A tremendous amount of internal processing is used for memory management. Emphasis should be on the efficient and economical use of storage and the CPU.

# Memory Terminology Background

- Random Access Memory: All words are equally accessible in same time. So time required for addressing and locating a word is constant and independent of its address. RAM is generally electronic (no physically moving parts) and fast.

- Direct Access Memory (or Cyclic Access): Stores information in a continuously repetitive loop. Each word is accessible only as it passes the reading/writing station. Access time is dependent upon the address or position of the data. Access times for cyclic stores is inherently longer since, on the average, half a cycle must elapse before the desired word becomes available at the read/write station. Cycle time is usually due to some mechanical movement time (e.g. rotational speed of disk).

- Sequential Access Memory: Data are read or written in a longitudinal serial fashion along a finite length of media (e.g. tape). Can have very long latency times.

- Basic goals of memory design:

- Minimize the impact of the processor / memory speed imbalance.

Generally, the CPU is much faster than (comparably priced) memory.

Want the system to run at processor speeds rather than at memory speeds.

Without instructions or data, CPU has no choice but to idle and wait.

[Present-day solution: Memory hierarchy, Cache memory]

- Provide "enough" memory for the processor at a cost-effective price.

Affects the extent to which the speed of the system is memory bound.

General rule:

A fast processor should have more memory than a slow processor.

Fast CPU can read and write more memory per unit time.

So, given same speed memory, faster CPU is more likely memory bound.

Fast CPU needs constant input of instructions and data to keep busy.

[Present-day solution: Virtual memory]

- Make memory optimization <u>automatic</u> without need for programmer intervention [Present-day solution: Memory management algorithms built into the OS]

- Note: All of above "solutions" must also inherently address cost, complexity, etc.]

- The Grand Design Challenge For Memory:

Find a memory architecture that is fast and large and cheap.

But no single memory architecture / technology can satisfy all three constraints.

Simple axiom of hardware design: Smaller is Faster.

Implication: It is impossible to build a memory that is large <u>and</u> fast <u>and</u> cheap. Fortunately, there is a saving grace: Principle of Locality.

# • Principle of Locality of Reference

The most important program property that enables designers to optimize memory.

Fact: The data most recently used is likely to be accessed again in the near future.

Programs tend to reuse data and instructions they have accessed recently.

Rule of thumb:

A program spends 90% of its execution time in only 10% of its code.

Favoring accesses to such a small set of data will improve performance.

Therefore, it is best to keep recently accessed items in the fastest memory.

i.e.) Put the 10% of highly used code in faster memory; the rest in slower mem.

This will give a speedup over the slower memory 90% of the time.

# Intuitive Justification of Locality of Reference for:

Instructions: Structured and Modular programming (esp. Loops, Subroutines).

Data: Matrices / Arrays and Record Data Structures.

# Two types of Locality:

- Temporal: Locality in Time.

If an item is referenced, it will tend to be referenced again soon.

e.g.) Loop Counter Variable.

- Spatial: Locality in Space.

If an item is referenced, nearby addresses will tend to be referenced soon. e.g.) Element i + 1 of the same matrix.

Note: An implication of locality is that, based on a program's recent past, one can predict what instructions and data it will need in the near future.

A good memory manager will make use of this 'predictive' capability.

Using locality of reference to our advantage, we can design:

- A Memory Hierarchy.

Which enables us to blend large, cheap, slow memories with small, expensive fast memories.

- A Memory Management Algorithm.

Which dynamically moves data to the proper "level" in the hierarchy as needed to optimize performance / cost.

# • Memory Hierarchy

A wide range of various memory technologies are available.

Each has variations (advantages/disadvantages) in terms of cost and performance. It is not economically (or technically) feasible to use just one type of memory.

Performance/Cost requirements vary tremendously within a computer system.

e.g.) Always used (OS), Frequently used (apps), Seldom used (archived data). Therefore, memory systems consist of a mixture of several different memory types.

### • Central Idea of a Memory Hierarchy:

Provide memories of various speed and size at different points in the system.

Organize the memory system into several levels by their speed, size, and cost.

Since smaller memories are faster, these should be located closer to the CPU.

These memories are the most costly on a per bit basis.

Memories become larger and slower as one moves away from the processor.

Lower cost per bit media can be used for levels furthest from the CPU.

Use a memory management scheme which will move data between levels.

Those items most often used should be stored in faster levels.

Those items seldom used should be stored in slower levels.

Ideally, this is done dynamically, automatically, and with little overhead.

- >> This is the job of the OS memory manager (the focus of our study).

- >> We will look at different memory management schemes.

# • A Typical Memory Hierarchy Consists of the following Levels:

### - Scratch Pad memory:

Consists of registers for control and arithmetic operations.

Accumulator, Program Counter (Generally on-chip).

Uses the fastest (and most expensive) semiconductor storage devices.

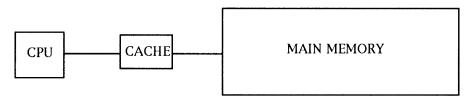

#### - Cache store:

Serves as a high speed buffer between slower main memory and CPU.

Technology and cost is between that of Main store and Scratch pad.

Note: Although cache is generally off-chip, some systems have on-chip cache.

# - Main Memory:

Holds current data and program being executed.

Uses fast, high capacity (lower cost) random access storage (e.g. core or LSI).

#### - Permanent Store:

Holds program/data not currently in use; available to main store on demand Requirement is for medium speed, high capacity, low cost storage.

#### - Mass Memory:

Used to store archival information.

High capacity, low speed, very low cost.

| Category         | Capacity (bits) | Access time | Access     | Technology |

|------------------|-----------------|-------------|------------|------------|

| Scratch pad      | 500-200K        | 5ns-10ns    | Random     | LSI        |

| Cache store      | 50K-200K        | 10ns-50ns   | Random     | LSI        |

| Main store       | 10K-10M         | 70 ns       | Random     | Core/LSI   |

| Perm. store      | 100M-1G         | 10 ms       | Direct     | Disks      |

| Mass store (old) | 10**9-10**12    | seconds     | Sequential | Tape       |

| Mass (new)       | 17 G            | 200 ms      | Direct     | CD-DVD     |

### Memory Management:

Using a pyramid structure, smaller memory is at top; larger memory is at bottom. The levels of the hierarchy generally subset one another.

All data in one level is also found in the level below it.

e.g.) A subset of disk is in RAM; A subset of RAM is in cache.

Hierarchy normally consists of many levels.

Technology can introduce new levels (e.g., Level 2 cache, CD, DVD) It is usually managed between two adjacent levels at a time.

Every pair of levels can be thought of as having an upper and lower level.

# Upper level:

Smaller and faster and more expensive memory.

Closer to the processor.

#### Lower level:

Larger and slower and less expensive memory.

Further from the processor.

An effective MM scheme would arrange the data in the hierarchy such that whenever the CPU needs to access storage, it is able to find the data it needs in the upper levels of the hierarchy the majority of the time.

- This would make the effective speed of the memory hierarchy nearly as fast as that of the fastest memory at the highest level of the hierarchy.

#### Hit ratio:

Percentage of memory accesses found in the upper level.

#### Miss rate:

(1.0 - Hit rate)

Since performance is main goal, speed of hits and misses is important.

Hit time: Time to access the upper level of the memory hierarchy.

Includes the time to determine whether the access is a hit or a miss.

Miss penalty: Time to move data in lower level up to a higher one.

If miss penalty is 10's of clock cycles, processor usually just waits.

If 1000's of clock cycles, CPU is task switched to another process.

A 1% decrease in hit ratio causes almost 10% drop in effective performance.

| Hit Ratio (%) | Effective MIPS |

|---------------|----------------|

| 100           | 5.0            |

| 9 9           | 4.4            |

| 98            | 3.9            |

| 97            | 3.6            |

| 9 6           | 3.3            |

| 9 5           | 3.1            |

| 90            | 2.2            |

- There are three issues when dealing with memory hierarchy management:

- 1) Placement: Where to put lower level information in the higher level

- 2) Replacement: What information in higher level to replace

- 3) Fetch: When to perform update of upper level with lower level

- Again, Locality enables a memory hierarchy, including cache memory, to work

Two empirical observations on program behavior are made:

- 1) Programs tend to reuse instructions and data.

- => Once information is requested from lower levels, it should be moved to upper level and be kept there as long as possible to let subsequent accesses to it be performed at the faster, upper level speeds.

Within loops, cache benefits are due to reusing previously accessed words.

- 2) Programs tend to use instructions and data near recently used instructions/data.

- => If a block of memory larger than what is immediately needed is moved to the upper level, this additional information is likely to be needed soon, and its presence in the upper level will save one or more future references to the lower level, thereby speeding up future references. In straight line code, cache benefits are due to lookahead effect of locality. In data access, cache benefits are due to sequential storage of neighbors.

- Although memory concepts apply between any two levels, Cache/MM is usual focus.

Cache Memory:

A small, fast "buffer" that lies between the CPU and the Main Memory (MM). It holds the Most Recently Accessed Data (and instructions).

Cache is generally only a small fraction of the size of main memory. Generally considered the first level in the hierarchy.

Registers and accumulators are considered part of the internal CPU.

[Note: Distinction is "blurred" since ICs today often include on-chip Cache] The term "cache" was coined by Conti.

First realization appeared in IBM System 360 Model 85.

Since then, caches have been present in most medium to large computers.

Idea: Provide a copy of recently accessed MM words in a fast cache memory.

Avoid accessing the slower main memory whenever possible.

Goal: Make effective memory speed run at full speed of cache.

Also make effective memory size as large as the entire main memory. High performance obtained by cache; Low cost obtained by lower levels (MM).

# • Cache Operates as follows:

When CPU needs to read/write to Main Memory, the cache is checked first.

If data is found in cache a hit occurs and memory works at cache speed.

If data not found, a miss occurs and memory works at the main memory speed.

Also, the data from MM is written to the cache.

#### Hit Ratio

Hit ratio is the number of processor requests satisfied by the cache divided by the total number of processor requests.

By definition, hit ratio is always less than or equal to 1.0 or 100%.

#### Define:

Hit Ratio = h = Probability that next memory access is found in the cache.

$T_a$  = Average effective memory access time as seen by CPU.

$T_C$  = Cache access time (access time for a hit).

T<sub>m</sub> = Main memory access time (access time for a miss).

Then effective memory time is:

$$T_a = hT_c + (1 - h) T_m$$

Speedup due to the cache is:

$$S_c = T_m / T_a$$

# - Example:

Assume MM access time of 100ns and cache access time of 10ns Hit ratio of 0.9 would give an average access time of:

$$T_a = .9(10ns) + (1-.9)(100ns) = 19ns$$

Speedup is:

$$S_c = 100 ns / 19 ns = 5.26$$

# - Example:

Same as above only hit ratio is now .95 instead:

$$T_a = .95(10ns) + (1-.95)(100ns) = 14.5ns$$

Speedup is:

$$S_c = 100 ns / 14.5 ns = 6.9$$

=>  $S_{C}$ , the speedup, is highly sensitive to small increases in cache hit ratio.

If h is low, cache memory will not be effective.

e.g.) If h = .5, we cannot achieve a speedup of more than 2, regardless of the speed of the cache.

Goal of Cache Memory is to run the system at close to processor speeds

The importance of getting high cache hit rates can be clearly seen

Need to achieve high cache hit rates (at least 90%-95% of the time)

Fortunately, typical hit ratios do range on the order of .9+

• Cache organizations differ primarily in the way blocks in MM are mapped to cache.

We examine three mapping schemes:

- 1) Fully Associative

- 2) Direct Mapping

- 3) Set Associative

For 1 and 3, Associative Mapping must be done fast since goal of cache is speed.

Must be able to search and find words (if present) in cache quickly.

Generally implemented in H/W using an associative (content-addressable) memory.

• Associative Memory or Content-Addressable Memory (CAM)

Accesses words based on their contents rather than their location (address).

Memory has extra hardware to perform fast search on its contents.

Parallel AND gate logic is employed to find matches against a key register.

- e.g.) "Retrieve all memory cells with data equal to value x."

- e.g.) "Retrieve all memory cells with x < data < y."

Small associative memories for management of caches have been built.

In cache, some address bits are stored along with data bits.

Match is performed on the address bits when a search is done.

"Does any cell in cache have this addresses' data? If so, what is the data?" Associative memory is extremely expensive because of parallel H/W match logic.

Limited by cost to be very small in size.

# • Fully Associative Mapping

A main memory block can map into any block in cache.

Theoretically optimum system: Fastest and most flexible.

Conceptually simplest form of cache organization.

Store both the entire MM address and its data in cache.

Each processor request requires a complete search of the cache.

When given a content value (address), CAM returns "associated" data.

Labels of all cells of the CAM are tested simultaneously to find a match.

# - Advantages:

No contention; a block of MM can be put in "best" cache cell possible.

# - Disadvantages:

Very expensive because of the required large CAM to perform matching in H/W. Search would be too slow if done by software.

Very wasteful of cache storage: Must store the <u>full</u> primary memory address.

**Main Memory**

| mani memery |     |        |  |  |  |  |  |  |  |

|-------------|-----|--------|--|--|--|--|--|--|--|

| Block 1     | 000 | Prog A |  |  |  |  |  |  |  |

| Block 2     | 001 | Prog B |  |  |  |  |  |  |  |

| Block 3     | 010 | Prog C |  |  |  |  |  |  |  |

| Block 4     | 011 | Prog D |  |  |  |  |  |  |  |

| Block 5     | 100 | Data A |  |  |  |  |  |  |  |

Cache Memory

| Block 1 | 100 | Data A |

|---------|-----|--------|

| Block 2 | 010 | Prog C |

Italics: Stored in Memory

### Direct Mapping

Opposite design extreme from fully associative; effectively a form of hashing. Cheaper to implement; no CAM memory required.

A subfield of the MM address is used to index the cache in the regular manner.

Least significant address bits are usually used for the index subfield.

Store higher order "tag" bits along with data in cache.

So, If MM Address is of form (t, i)

then i bits designate the index to the cache block (the cache address)

t bits are used for the tag

The number of i bits needed depends on size of cache (e.g., i=3 if size = 8).

Several MM words can have same i bits; Only one can be in cache at a time.

Hit occurs only if tag at indexed cache location matches desired MM address tag.

This allows consecutive blocks to reside simultaneously in cache but,

All of the addresses in MM with same i subfield must share cache space. Assume Cache has K blocks:

Main Memory blocks are effectively mapped into cache block via MOD function.

Cache block = (Main memory block number) MOD (K)

e.g.) Suppose Cache has K = 4 blocks and Main memory has 8 blocks.

So Main Memory blocks 1 and 5 would map into cache block number 1.

Only one MM address bit (MSB) needs to be stored in cache as tag.

Main Memory

| mann memery |     |        |  |  |  |  |  |  |  |

|-------------|-----|--------|--|--|--|--|--|--|--|

| Block 1     | 000 | Prog A |  |  |  |  |  |  |  |

| Block 2     | 001 | Prog B |  |  |  |  |  |  |  |

| Block 3     | 010 | Prog C |  |  |  |  |  |  |  |

| Block 4     | 011 | Prog D |  |  |  |  |  |  |  |

| Block 5     | 100 | Data A |  |  |  |  |  |  |  |

| Block 6     | 101 | Data B |  |  |  |  |  |  |  |

| Block 7     | 110 | Data C |  |  |  |  |  |  |  |

| Block 8     | 111 | Data D |  |  |  |  |  |  |  |

| Block 8     | 111 | Data D |  |  |  |  |  |  |  |

Cache Memory

| Block 1 | 00  | 0 | Prog A |

|---------|-----|---|--------|

| Block 2 | 0 1 |   |        |

| Block 3 | 10  | 1 | Data C |

| Block 4 | 11  | 0 | Prog D |

Italics: Sto

Stored

in

Memory

#### - Potential Problem:

Suppose cache is 4 blocks and Main Memory holds 4 program + 4 data. Excess swapping occurs if Prog A reads/writes Data A in a loop.

#### - Disadvantage:

Contention with MM data with same index bits.

#### - Advantage:

Low cost; doesn't require an associative memory in hardware.

Don't need to store low-order i bits of MM address label in cache memory.

Saves valuable cache space since MM i bits equal the cache's address.

### • Set Associative Mapping

Intermediate, compromise solution between Fully Associative and Direct Mapping. Maintains simplicity of the direct mapping approach.

Not as expensive and complex as a fully associative approach.

Allows for some flexibility in block placement.

Not as much contention as in a direct mapping approach.

Technique: Put a fully associative cache within a direct-mapped cache.

Organize the cache into K sets; Let each set contain P blocks.

MM address is directly mapped modulo K (via i bits) into a specific cache set.

But, it can be placed associatively in any of the P cache blocks within that set.

Typically, P (the number of "ways" or "degrees" in a set) is kept between 2 and 8.

Solves the contention problem in previous example with pure direct mapping:

Can put MM segments Prog A & Data A in different blocks within the same set.

Main Memory

| Block 1 | 000 | Prog A |

|---------|-----|--------|

| Block 2 | 001 | Prog B |

| Block 3 | 010 | Prog C |

| Block 4 | 011 | Prog D |

| Block 5 | 100 | Data A |

| Block 6 | 101 | Data B |

| Block 7 | 110 | Data C |

| Block 8 | 111 | Data D |

|         |     |        |

| Cac | he | Me | mo | ry |

|-----|----|----|----|----|

|-----|----|----|----|----|

| Set 1 | 0 | 00 | Prog A | 10 | Data A |

|-------|---|----|--------|----|--------|

| Set 2 | 1 | 11 | Data D | 10 | Data B |

# - Advantages:

A generalized version of both fully associative and direct mapping.

Total number of cache blocks = N = KP.

If P = 1, then this is just direct mapping.

If P = N = entire cache size, then this is just fully associative mapping.

Main cost is in the complexity ("degrees") of the associative memory.

Statistical Hit/Miss rate as a function of P:

| Degree Associativity | Miss Rate |

|----------------------|-----------|

| 1-way                | 6.6%      |

| 2-way                | 5.4%      |

| 4-way                | 4.9%      |

| 8-way                | 4.8%      |

=> Degree of associative search need not be over more than 2 to 8 tags. Performs close to theoretical optimum of a fully associative approach.

Cost is only slightly more than a direct mapped approach.

Set-Associative cache offers best compromise between speed and performance. The most favored design among manufacturers.

### Replacement Algorithm:

Since the cache memory is very small, it is usually kept full.

Eventually, a new block from MM will need to be brought into a full cache.

Replacement algorithm determines which block in cache is removed to make room.

- Direct mapping:

Replacement algorithm is trivial: No choice.

- Fully Associative:

Many alternatives for replacement: Can choose over whole cache.

- Set-Associative:

Some freedom: No choice of set but can choose within a set.

For fully and set-associative, a wide range of replacement algorithms is possible.

However, complex replacement algorithms may be too difficult to implement.

The decision of which block to replace has to made very quickly (nanoseconds).

Maximize hit ratio by preserving in cache the elements that are in locality of ref.

# • Two main policies in use today:

- Least Recently Used (LRU) Algorithm.

Attempts to reduce chance of throwing out block that will be needed soon. Accesses to blocks are recorded.

The block replaced is the one unused for the longest time.

e.g.) Attach an age counter (usually via hardware) to each block.

When a block is loaded into cache, set its counter to 0.

When a hit occurs for a block, also set its counter to 0.

Bump counter for all other not-used blocks on each access by 1.

If cache is full on a miss, remove the block with highest counter value.

Becomes increasingly expensive to implement as number of blocks grows.

Most popularly used (e.g. IBM 360 family).

#### - Random

Clark in 1983 showed only a small penalty for using Random instead of LRU.

A counter-intuitive empirical result.

Trivial to implement (e.g., random number generator).

Used in DEC VAX 11 family.

| Cache<br>Size | Miss Rate:<br>LRU | Miss Rate:<br>Random |

|---------------|-------------------|----------------------|

| 16KB          | 4.4%              | 5.0%                 |

| 64KB          | 1.4%              | 1.5%                 |

| 256KB         | 1.1%              | 1.1%                 |

=>> The Replacement policy used becomes less important for larger caches. If there are more blocks to choose from, the choice is less critical. Probability of replacing the block that's needed next is relatively low.

• Handling Memory Writes with Cache:

Writes generally take longer than reads.

Fortunately, reads dominate cache accesses.

All instructions are reads, and most instructions don't write to memory.

Typically, read to write ratio is 10 to 1 (Writes occur only 10% of the time).

Where should the data written out by the CPU be stored?

Three mutually exclusive ways the system can proceed:

1) Write-Through or Store-Through

Writes updated data to both the cache and main memory simultaneously. Makes action upon replacement simple:

When cache block is replaced, block is just flushed.

Ensures that the cache and MM entries are always the same.

Can result in unnecessary Write operations being performed to the MM.

Esp. if same cache word is updated many times during its residency.

Consecutive writes will result in T avg. approaching the slower MM rates.

2) Write-Back, Write-out, Copy back, or Store-to-cache approach.

Update the cache location only and mark it as being "dirty" (modified).

Requires an extra bit to be associated with each cache block.

If the block is currently not in cache, then move it there before writing.

When a block needs to be removed from cache, it can be:

- 1) Discarded if it is still "clean".

- 2) Written back to MM if it is marked as being "dirty".

More universally popular than Write-Through Method.

3) Store-Wherever approach

If copy resides in cache, then only that copy is updated.

Requires "dirty" bit to identify the block for write-back when replaced.

If no copy resides in cache, only the main memory is updated.

Element is not moved into the cache on a write.

Ignores locality with writes.

- Other Parameter that affect Performance of Cache memory:

- Size of the Block transferred from MM to cache:

Large blocks result in less overhead.

Easier to fetch one 8-word block than fetch eight 1-word blocks.

Also Maximizes benefits of spatial locality.

Small blocks only move in the data actually needed; results in less waste.

- Size of the Cache:

Larger cache will generally increase hit ratio asymptotically.

Larger cache will enable larger sized blocks to be used.

=> Using a cache is more economical than using fast memory devices for the entire MM.

- Primary goal of Cache Memory is to increase Speed

Requires memory hierarchy management between cache and MM RAM.

- Primary goal of Virtual Memory is to increase Space

Requires memory hierarchy management between MM RAM and disk.

- Virtual Memory:

- Parallels many of the ideas of cache memory.

- e.g.) General problem of deciding which block is to be removed from a full MM is similar to deciding which block to remove from cache.

Concepts like LRU replacement algorithm can be applied to page replacement.

Cache management is usually handled by simple algorithms (must be very fast).

Virtual memory management can be more sophisticated (lower in hierarchy).

- Addresses two key issues:

- Computer users often want more MM than is physically present in machine. Second generation machines required manual memory overlays. Programmer had to identify mutually exclusive memory reference areas. Programmer could bring only one area into MM at any one time. Labor intensive: 50% of development time was spent implementing overlays.

- 2) Time Sharing systems need automatic dynamic memory relocation capability. System serves multiple users "concurrently".

Not every user's program or data need be in MM at the same time.

Slow I/O response times (e.g. human) enabled processes to be swapped.

A swapped out program is "suspended" in mid-execution and moved out of MM.

On swap-in, it may be better to place program in a different memory location.

Also, Parts of the same program can be in different memory locations. Block allocation can be done without regard to maintaining contiguity.

Reduces need to rearrange memory when process population changes.

Results in a noncontiguous and nonsequential dispersion of program(s) in MM.

Portions of a program that appear to be contiguous may not be physically.

Could be scattered throughout the memory in different block locations.

Enables the OS to make maximum use of memory space.

A small physical location can be used for a large virtual address space. Reduces occurrence of fragmentation.

### Fragmentation:

A phenomenon which can cause wasted memory at any level of hierarchy. When a large percentage of memory becomes small slots (fragments). The slots are not contiguous and therefore, are too small to be useful.

A time-consuming "garbage collection" process can be used to amalgamate the many small slots into a larger, more useful area.

Fragmentation can result from:

- Roundoff in block allocation.

- Growing and contracting data areas.

- Programs entering and leaving the multiprogramming mix.

- Repeatedly deleting and adding various sized files (disk frag.).

- Underlying concept of Virtual Memory:

Program and data are assigned addresses independent of:

- The amount of physical MM storage actually available.

Addresses Space issue (1) above.

- The location from which the program will actually be executed.

Addresses Dynamic Relocation issue (2) above.

Program and data both reside in virtual memory space.

Memory Management unit moves data into and out of MM RAM from disk.

The units of data transfer and replacement (blocks) are called pages or segments.

• Dynamic Address Translation (DAT):

Mapping: The correspondence between virtual storage and physical storage. A mapping table enables DAT to occur.

Virtual address is mapped to a physical address via the mapping table. Relocates a program and its data segments in real time.

Translation is done transparently and "on the fly" (dynamically). Does not require modifying the addresses within the program's instructions. Requirements for the DAT mechanism:

- Fast Mapping

Mapping function must be simple to compute in negligible time.

- Fast Update

When block is relocated, tables must be updated quickly.

- Fast Context Switching

When CPU switches processes, new mapping must engage quickly.

- Efficient Memory Hierarchy Management

Hit rate should be maximized and time for miss penalty minimized.

- Efficient Usage of Physical Memory

Achieve intensive use of memory by avoiding fragmentation.

# Minimizing Overhead:

If mapping table itself were kept in RAM, then performing the DAT would cost an entire extra RAM memory cycle time. (Table + Element lookup).

Translation Lookaside Buffer (TLB) performs mapping.

Special hardware generally used to accelerate table lookup process. Small associative memory and possibly fast adders.

### • Two Ramifications of Virtual Memory

### 1) Addressability

Program can form addresses larger than the range of real physical memory. Frees programmer from concerns about fitting programs into available memory. Illusion is created by both the processor hardware and the virtual memory OS. Programmer has the conceptual ability to treat the memory as if it were:

- Infinite in size

- Always there

# 2) Relocatability

No direct relationship b/w addresses used by a prog and their physical locations. No linear ordering relation is implied by blocks in physical memory.

Virtual address 5700 > 4500 sequentially; but not necessarily in physical mem. Disassociates an address from a memory location.

System / maintenance programmers must be aware of relocatability.

e.g.) A "different" memory location fails every time a program is run.

Program can be scattered throughout memory.

Core dump must be interpreted.

Contents of memory at any one time is a collection of disjoint blocks.

- Three block-oriented mapping schemes for virtual memory:

- Paging

Simplest method of virtual to physical translation.

Page: A fixed size block of virtual address space.

All pages are therefore the same size.

Typical page sizes range from 512 bytes to 4K bytes.

Page Frame (or Slot): Block of physical memory space.

Any page can be stored in any page frame.

An address x generated by CPU is partitioned into high and low order bits.

High order bits are treated as a page number.

Low order bits are treated as an offset within the page.

Address translation is just substitution of page frame number for page number.

- External fragmentation problem is solved.

Each page will exactly fit in a page frame.

- However, fixed-size pages can lead to internal fragmentation.

- e.g.) Assume page sizes of 4K bytes and a program size of 13K bytes

Results in 4 assigned pages (16K bytes) wasting 3K in the last page.

If too few slots are allocated to a program, thrashing occurs.

Thrashing: Constant movement of the same blocks between two levels. If severe, can lead to deadlock where no process can proceed.

### Segmentation

Paging is concerned with the partitioning of physical storage space.

Pages assume a predetermined relationship to blocks of physical storage.

Segmentation is concerned with the allocation of <u>functional</u> space.

Segments are viewed as logical subdivisions of virtual storage.

Example segments: procedures, subroutines, matrices, data structures.

# A segment is:

- 1) An independent linear address space.

- 2) Variable in size as opposed to fixed in size as pages.

Size of each block must be explicitly recorded in the mapping table.

### Segments enable:

- -Data structures to expand and contract.

- -Protection.

Programs (read only) can be in separate segments from data (R/W).

-Sharing in multiprogrammed systems.

Multiple processes executing same program can use same segments.

Several users may be executing same program with different data.

Their data is loaded into different areas of physical storage.

But they can share a single copy of the program in physical mem.

Pointers set to same location via the mapping mechanism.

No internal fragmentation occurs using variable sized Segments.

External fragmentation can occur unless contiguous blocks are relocated.

Segments normally require contiguous storage locations in MM.

Since segments are variable size, range in sizes can be rather large.

Therefore, even if some empty regions exist, they may not be usable.

# Segmentation with Paging

Let each segment define a linear memory space which itself is paged.

Segmentation is applied to the user's virtual space.

Paging is applied to the real physical memory space.

Each segment can contain a variable number of fixed size pages.

Accrues the advantages of both segmentation and paging.

A compromise on the size of Allocated Memory:

Large blocks are good because it keeps the translation table small.

However, only a small number of blocks can be allocated.

Limits the number of users or applications that can be serviced.

Small blocks can service many users or applications concurrently.

But requires a large translation table.

=> Use Large blocks (segments) partitioned into smaller blocks (pages).

Requires a double look-up on two tables (a segment table and a page table).

# • Replacement Algorithms for Virtual Memory:

Similar to Cache replacement algorithms, but can be more complex in S/W.

# • Optimal Replacement

Replace the page which will not be used for the longest (future) period of time.

A theoretically 'best' page replacement algorithm for a given fixed size of VM.

Produces the lowest possible page fault rate.

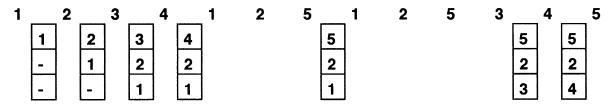

Example: Assume the following page reference string w/ 3 frames of allocated VM.

Faults are shown in boxes; hits are not shown.

Seven page faults occur.

Generally impossible to implement, since it requires future knowledge of ref. string. Merely used to gauge the performance of real algorithms against best theoretical.

#### • FIFO

Simplest page replacement algorithm.

Can be implemented with a simple shift mechanism (or a head/tail queue).

Needs no knowledge of reference string (past or future).

When a page fault occurs, replace the one that was brought in first.

Example: Assume the following page reference string with 3 frames of allocated VM.

Nine page faults occur.

Problem: Performance may not always be good.

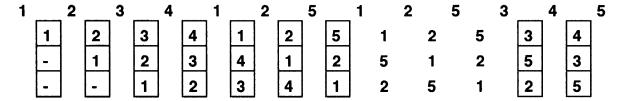

Can exhibit inconsistent behavior known as Belady's anomaly.

Number of faults can increase if job is given more virtual memory.

Example: Same reference string as above only with 4 frames instead of 3

| 1 |   | 2 |   | 3 |   | 4 |   | 1 | 2 | 5 |   | 1 |   | 2 |   | 5 | 3 |   | 4 |   | 5 |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   | 1 |   | 2 |   | 3 |   | 4 |   |   |   | 5 |   | 1 |   | 2 |   |   | 3 |   | 4 |   | 5 |

|   | - |   | 1 |   | 2 |   | 3 | 2 |   |   | 4 |   | 5 |   | 1 |   |   | 2 |   | 3 |   | 4 |

|   | - |   | - |   | 1 |   | 2 |   |   |   | 3 |   | 4 |   | 5 |   |   | 1 |   | 2 |   | 3 |

|   | - |   | - |   | - |   | 1 |   |   |   | 2 |   | 3 |   | 4 |   |   | 5 |   | 1 |   | 2 |

Ten page faults occur.

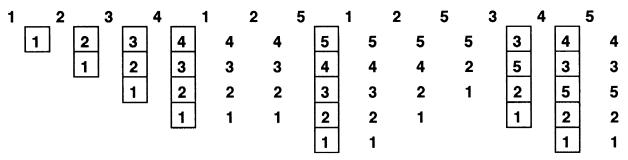

### • Least Recently Used

Replace the page which has not been used for the longest period of time.

Can use either a counter or a stack mechanism.

Example: Using a stack with 3 frames of allocated VM (keeping most recent on top). Faults shown in boxes; hits only rearrange stack.

Nine page faults occur.

LRU is more expensive to implement than FIFO, but is more consistent.

Does not exhibit Belady's anomaly, since by induction:

For n pages, LRU keeps the n most recently referenced pages in memory.

For n+1 pages, LRU still keeps the subset of n most recent pages in mem.

More overhead needed since stack must be updated on each access.

LRU generally gives better performance since temporal locality is preserved.

Example: Same reference string as above only with 4 frames instead of 3.

| 1 |   | 2 |   | 3 |        | 4 |   | 1 |   | 2 |   | 5 |   | 1 |   | 2 |   | 5 |   | 3 |   | 4 |   | 5 |

|---|---|---|---|---|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   | 1 |   | 2 |   | 3<br>2 |   | 4 |   | 1 |   | 2 |   |   |   | 1 |   | 2 |   | 5 |   | 3 |   | 4 |   |

|   | - |   | 1 |   | 2      |   | 3 |   | 4 |   | 1 |   |   |   | 5 |   | 1 |   | 2 |   | 5 |   | 3 |   |

|   | • |   | - |   | 1      |   | 2 |   | 3 |   | 4 |   | 1 |   | 2 |   | 5 |   | 1 |   | 2 |   | 5 |   |

|   | - |   | - |   | -      |   | 1 |   | 2 |   | 3 |   | 4 |   | 4 |   | 4 |   | 4 |   | 1 |   | 2 |   |

Seven page faults occur.

# • Fixed Partitioning vs. Dynamic Partitioning

Want to maximize number of jobs in a multiprogrammed, virtual memory.

Increases probability that job scheduler can find a job not in I/O or wait state.

More alternatives for process switching.

Maximizes throughput and overall system performance.

Increases total number of jobs processed per unit time.

Minimizes total space-time product.

Decreases amount of memory a job needs and the total time it needs it for.

- Fixed size virtual memory allocation.

LRU, Random, FIFO are all fixed size allocation methods.

A job is given a fixed allocation of virtual memory while running.

Needs to be "burned in" at design time (either as a H/W or S/W parameter).

Fixed size allocation schemes are also extremely hard to optimize.

If space allocated to each job is too small, thrashing occurs.

If too much memory is allocated, space is wasted.

A wide mix of programs with wide range of memory requirements exist.

Memory requirements of a job can change over its run time.

Want self-adaptive virtual memory size allocation schemes.

More sophisticated replacement policies dynamically adjust allocated VM RAM.

The number of page frames per process varies during execution.

This will minimize the memory space-time product and maximize throughput.

Two popular algorithms:

- 1) Working Set (WS)

- 2) Page Fault Frequency (PFF)

If respective parameters are properly adjusted, WS and PFF are similar in perf.

Both are generally better than fixed size LRU.

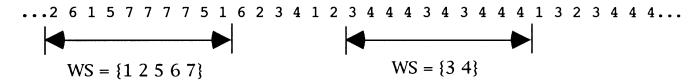

## Working Set

Denning 1968.

Working set is the minimum amount of space required for a program to perform well. A working set is the set of distinct pages most recently referenced by a program. Uses a working set window defined by T.

Requires looking back at the last T references in the page reference string.

Remove page frame whenever it has not been referenced during last T references.

As a program executes, it moves from locality to locality.

A locality is a set of pages which are actively used together.

e.g.) Entering a subroutine brings in its locality of instructions, variables, etc.

Upon exit, the pages associated with this locality are no longer needed.

Try to detect and preserve in RAM the dynamic locality set of a program in execution.

If enough pages are allocated to a job's newly entered locality,

it will fault until all of the pages of this locality are in memory,

then it will not fault again until it changes localities again.

Performance of the working set algorithm depends upon the selection of T.

If T is too small, it will not encompass the entire working set (thrashing).

If T is too large, it will overlap several localities (wasting space).

Essentially a generalization of LRU.

Any page not referenced in window size T can be replaced; not just the LRU. Overhead is associated with keeping track of the working set.

Working set is essentially a moving window.

A page is in the working set if it is referenced anytime during last T references. Interesting note: A page is not necessarily replaced at page fault time.

It may just move out of the 'window' upon a hit of another page.

- Example: Using a window of T = 10.

Number of pages allocated would be five at one point, then two at another.

- Example: Using a window T = 6

Note: Not really a stack algorithm (order on stack not significant).

Seven page faults occur.

Space-Time product (assuming time between references are equal):

Integrate (sum) memory cells used over time (in this case, let each time = 1): 1 + 2 + 3 + 4 + 4 + 4 + 5 + 5 + 4 + 3 + 4 + 5 + 5 = 49.

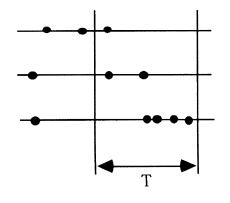

• Page Fault Frequency (PFF)

Chu 1974.

Since goal of dynamic allocation is to reduce thrashing, measure page fault rate.

Thrashing is simply a high page fault rate; so want to control PFF.

Establish an upper and lower threshold bound on the desired page fault rate.

If fault rate is too high, the process needs more frames.

Increase its allocation.

If fault rate is too low, process may have too many frames allocated to it.

Decrease its allocation.

This will free up frames for other processes in a multiprogrammed system.

- Example: Time line showing page faults (assume target PFF is 2 faults per T).

Three different jobs; three different situations.

Decrease virtual memory allocation (PFF below threshold)

Acceptable PFF w/in a T time window

Increase virtual memory allocation (PFF above threshold)

### - Example:

Upper threshold: Add a page frame if current page is a fault and last one was a fault. Lower threshold: Remove a page (LRU) if this is the third ref. in a row w/o a fault.

| 1 _ | 2 |   | 3 |   | 4 |   | 1 |   | 2                     | 5 |   | 1 | 2 |   | 5 |   | 3 |   | 4 |   | 5 |   |

|-----|---|---|---|---|---|---|---|---|-----------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|

|     | 1 | 2 |   | 3 |   | 4 |   | 1 | 2                     |   | 5 | 1 |   | 2 |   | 5 |   | 3 |   | 4 |   | 5 |

|     |   | 1 |   | 2 |   | 3 |   | 4 | 1                     |   | 2 | 5 | 5 | 1 |   | 2 |   | 5 |   | 3 |   | 4 |

|     |   |   |   | 1 |   | 2 |   | 3 | -<br>2<br>1<br>4<br>3 |   | 1 | 2 | 2 | 5 |   | 1 |   | 2 |   | 5 |   | 3 |

|     |   |   |   |   |   | 1 |   | 2 | 3                     |   | 4 | 4 | , | 4 |   |   |   |   |   | 2 |   | 2 |

Seven page faults occur.

# • Finding the frames to allocate.

Free cells are usually kept on a linked list.

When the empty cells vary in size, first cell may not be large enough nor optimal.

Many algorithms exist for performing cell allocation.

Need to compromise b/w the computational cost of finding a cell and its optimality. Optimality depends on the rate of fragmentation.

# - Three examples:

# 1) Best Fit Strategy

Requires a search of all cells available for allocation.

Pick the one that is the correct size or is the smallest that is large enough.

# 2) First Fit Strategy

Scans the list and then allocates the first cell that is large enough.

Requires minimal computation, but may promote fragmentation.

# 3) Buddy System Strategy

Based on the hypothesis that the sizes of cells requested are not random.

Assumes if a cell of size x is needed, other cells of size x will also be needed.

If size x requested, the next larger power of two size cell is actually allocated.

A future request for a cell the same size can then be found without a search.

It is just the address of the neighboring cell (the other half allocated).

Knuth (1968) performed simulation studies.

Buddy system is best of three above.

Knuth also found: First fit algorithm is superior to the best-fit algorithm.

Best fit will search for closest available cell to that needed.

Remaining leftover space is guaranteed to be small.

Definition of "best".

Results in fragmentation.

Many small useless cells are eventually left.

- Other Frame Allocation Schemes:

- Many "Improved" versions of Buddy Scheme exist.

These generally try to reduce the amount of resulting internal fragmentation.

- Next Fit: A variation of First Fit.

Searches from where it left off, instead of at beginning of free memory list. Gives worse performance than First Fit.

- Worst Fit: Opposite approach of Best Fit.

Tries to leave the biggest hole available so that it might be useful later. Empirically shown to be bad.

- Formal definitions of Swapping vs. Demand Paging

- Swapping:

All pages of a program are loaded into memory blocks when the program beings Thus, in order to start, all of the program must be contained in memory.

- Demand Paging:

A program is started when some minimum space is available.

Additional pages are brought into memory only when they are needed.

- Most systems today are Demand Paging, but also informally called "Swapping".

# • RAM Memory Terminology

- Cycle Time: The speed with which consecutive blocks of words may be written into or read out of memory. Defined as the minimum time between successive references to storage. Consists of the access time plus a waiting (or refresh) time.

- Access Time: The interval between arrival of the signal activating memory and the completion of write-in or read-out.

- Waiting time: The "resting period" or the time the storage device needs to settle sufficiently before the next reference to it can be performed. Especially needed for RAM (a destructive dynamic memory) which requires memory cells just read to be refreshed.

- Dynamic Storage: Uses continuous recirculation of some physical quantity.

- Volatile Storage: Loses the stored information with time or power-off.

e.g.) Capacitive memory cell requires power to maintain charge.

- Destructive Read-Out: Process of reading information effectively destroys it.

Data then needs to be restored or refreshed.

- e.g.) Capacitive memory cell gets discharged when it is read.

- Most semiconductor LSI memory chips are dynamic, volatile, and destructive.

They require a waiting or refresh time as an inherent part of their cycle time.

Good memory management reduces the perceived impact of RAM refresh times.

• Memory Interleaving: Divide memory into a number of separate banks.

Goal: Avoid CPU idle during wait (restore/refresh) portion of memory cycle time.

Various degrees of interleaving architectures are possible ("k-way" interleaving).

e.g.) If memory is four-way interleaved, four separate memory banks exist.

Each contains one-quarter of the total words in memory.

It is common to divide the words in the banks using a modulo function.

e.g.) If 4-way interleaving is used, words 1, 5, 9... will be in bank one.

Assume the CPU can overlap requests between banks (typically so).

Thus, while a fetch or restore is in progress for a word in one bank,

a word from a different bank may be fetched.

CPU should issue requests for words before these words are actually needed.

Mainly useful for words in a straight-line program segment (i.e. instructions).

Operands (data) normally results in out-of-sequence requests to memory.

In this way, it is possible to access consecutive words of memory rapidly.

Interleaving can have a dramatic effect on the average effective speed of memory.

Consider a memory consisting of k modules.

Effective cycle time:

Decreased by a factor k if all k modules are kept busy continuously.

Varies depending upon the program and bank arrangement.

Speedup is usually in the range of SQRT(k) to k.

Number of modules usually range from 16 to 32.

e.g.) Assume a new fetch can be started when previous fetch is half completed.

This assumption is reasonable because cycle time = access + wait time.

Access Time can typically equal Wait Time

Access Time can typically equal Wait Time.

Then, with interleaving, memory will seem to operate twice as fast.

# Implementation:

A module is selected by the low-order (log<sub>2</sub> k) bits of the MM address.

The high-order bits determine the location within that module.

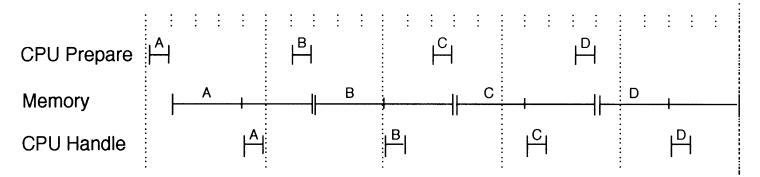

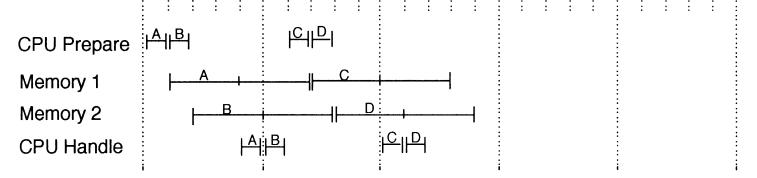

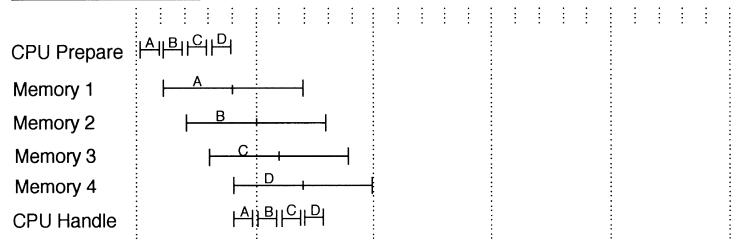

### • Example:

Assume that Memory has a 0.6  $\mu s$  Access Time and 1.2  $\mu s$  Cycle Time.

The CPU takes 0.2  $\mu s$  to prepare a memory request and 0.2  $\mu s$  to process the result.

The CPU can either prepare a memory request or process a result in parallel with the memory. The CPU can issue a request for an operand (e.g. B) before actually receiving and processing a previously requested operand (e.g. A).

The total time needed by the overall system to perform an operation spans the time between the CPU's preparation of the very first memory request to the time when the CPU completes processing of the last memory request.

Four operands, A thru D are to be retrieved from memory and processed.

# Non-Interleaved:

Total Time = 4.6  $\mu$ s CPU Utilization = 8 / 23 = 34%

# Two-Way Interleaved:

Total Time = 2.4  $\mu$ s CPU Utilization = 8 / 12 = 66% Speedup over Non-Interleaved = 4.6 / 2.4 = 1.9

# Four-Way Interleaved:

Total Time = 1.6  $\mu$ s CPU Utilization = 8 / 8 = 100% Speedup over Non-Interleaved = 4.6 / 1.6 = 2.8 Speedup over Two-Way Interleaved = 2.4 / 1.6 = 1.5

• Interleaved memory makes contiguous block transfers very efficient.

So, transferring data in blocks from the MM to the cache can be done quite fast.

• Data Arrangement in Interleaved Memory

Interleaved memory works best with sequential addresses (e.g. instructions). Optimization can also be performed for data accesses (e.g. matrices).

Best arrangement varies with dimensions of matrix; we look at one example. Typical operations on a matrix involve access to rows, columns, and diagonals.

- Arrangement 1: "Straight" Storage Scheme across 4 Modules

| M 1   |

|-------|

| A(00) |

| A(10) |

| A(20) |

| A(30) |

| M 2   |

|-------|

| A(01) |

| A(11) |

| A(21) |

| A(31) |

|       |

| M3    |

|-------|

| A(02) |

| A(12) |

| A(22) |

| A(32) |

|       |

| M 4   |

|-------|

| A(03) |

| A(13) |

| A(23) |

| A(33) |

Allows access to Rows and Diagonals without conflict Conflict on Columns (e.g. A(y2) are all be read from M3 while M1, M2, M4 are idle).

- Arrangement 2: "Skewed" Storage Scheme

Barrel shift each row by an increasing amount

Row 0: No Shift; Row 1: Shift Right One; Row2: Shift Right Two ....

| M 1   |

|-------|

| A(00) |

| A(13) |

| A(22) |

| A(31) |

| M 2   |

|-------|

| A(01) |

| A(10) |

| A(23) |

| A(32) |

| М3    |  |  |  |  |  |  |

|-------|--|--|--|--|--|--|

| A(02) |  |  |  |  |  |  |

| A(11) |  |  |  |  |  |  |

| A(20) |  |  |  |  |  |  |

| A(33) |  |  |  |  |  |  |

| M 4   |

|-------|

| A(03) |

| A(12) |

| A(21) |

| A(30) |

Allows access to Rows and Columns without conflict. (Minor) Conflict on Diagonals.

- Arrangement 3: "Two's Skewing" Storage Scheme

Barrel shift each row by two

Insert an extra module; Skip one module per row (wasteful of memory cells)

| M 1   |

|-------|

| A(00) |

| A(13) |

| A(21) |

| -     |

| M 4   |  |

|-------|--|

| A(03) |  |

| A(11) |  |

| -     |  |

| A(32) |  |

| M 5   |

|-------|

| -     |

| A(12) |

| A(20) |

| A(33) |

Allows access to Rows, Columns, and Diagonals without conflict.

# Memory Summary:

Future may bring larger and faster memories.

CPUs might possibly have speed matched memories at comparable costs.

This would reduce the need for memory hierarchies and cache memory.

Might also eliminate the need for virtual memory (giga-byte RAM chips).

Processors without a memory hierarchy would be simpler since:

- All Memory accesses would always take the same amount of time and

- No memory management overhead would be necessary

### • I/O Device Management

Disk Drive and Tape Drive Units generally consist of two components:

1) Mechanical

The actual physical device itself (e.g. the disk drive).

2) Electronic

The device controller or adapter (e.g. a circuit card).

• Operating System always deals with the controller; not the actual device.

Each controller has registers used for communicating with the CPU.

OS performs I/O by writing commands into the controller's registers.

After command is issued, CPU can swap to another process.

Controller issues interrupt to CPU when I/O is completed.

- An important function of the controller is internal buffering.

Controller converts serial bit stream from device into block of bytes.

When system bus is ready, the block is (DMA) transferred to main memory.

Mechanical device (e.g. disk) usually stays in motion.

Controllers cannot perform input and output at same time.

Cannot fill its buffer and write its buffer to main memory concurrently.

Thus, data cannot be read from physical device while writing to main mem.

Controller can only read every other block on the disk.

(Assuming disk read time = main memory write time).

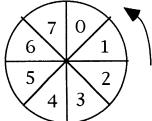

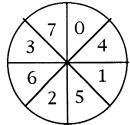

Therefore, disk formats must be interleaved to allow controller to write to MM.

If main memory write time > disk read time, larger interleave factors required.

Allows OS to read consecutively numbered blocks at max mechanical device speed.

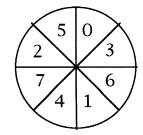

Examples of various degrees of Interleaving:

Non-Interleaved

Single Interleaved

Double Interleaved

### • Disk Arm Scheduling Algorithms

Time needed to read or write a disk block is determined by three factors:

1) Seek Time

Time to move arm to proper cylinder (track).

2) Rotational Delay (Latency Time)

Time for the proper sector to rotate under the head so reading can begin.

Disks usually rotate at about 3600 RPM (one rev per 16.7 msec).

On average, rotational delay is 1/2 a revolution (8.3 msec).

3) Transfer Time

Time to read and transfer the data of interest.

Transfer time = Rotation Time \* [(Bytes Transferred) / (Bytes per Track)]

Seek Time is the most significant of all three above.

Seek Time typically greater than Rotational Latency Time.

Read arm must be accelerated and decelerated accurately to proper cylinder. Scheduling algorithms concentrate on reducing Seek Times.

Several disk read requests can arrive during the span of just one seek time. Also, assume a multiprogrammed system.

Many different processes may be generating requests to the same disk.

Processes may do accesses to disk at different frequencies.

Disk does not see Temporal Locality

Several different localities of references are getting mixed.

Disk does not see Spatial Locality

Requests are effectively random.

Maintain a linked list entry for all pending cylinder number read requests.

Goal of Disk Arm Scheduler is to Analyze pending read requests and

perform some kind of optimization in terms of which request to handle next.

We examine three disk algorithms as a prelude to processor scheduling algorithms. Desirable Characteristics of a Scheduling Policy:

**Fairness**

Throughput

Mean Response Time

Variance in Response Time (i.e. Predictability)

# • First-Come, First-Served (FCFS)

Disk Driver accepts requests one-at-a-time and handles them one-at-a-time. Requests are processed in the order received (no reordering of the queue).

## - Example:

| Order Received: 11  |     | 1 |     | 40 |    | 16 |    | 3 4 |    | 9 |   | 1 2 |     |

|---------------------|-----|---|-----|----|----|----|----|-----|----|---|---|-----|-----|

| Order Processed: 11 |     | 1 |     | 40 |    | 16 |    | 3 4 |    | 9 |   | 1 2 |     |

| Cylinders Traveled: | 1 0 | _ | 3 9 | _  | 24 | +  | 18 | +   | 25 | + | 3 | _   | 119 |

Advantage: Simple to implement.

Fair to all requests.

Performs acceptably if load is light.

Disadvantage: No optimization.

Can exhibit a random seek pattern.

Successive requests can cause seeks from innermost to outermost cylinders.